# SRI G.C.S.R COLLEGE

(Affiliated to Dr. B. R. Ambedkar University, Srikakulam) GMR Nagar, Rajam – 532127, Srikakulam (Dist.), A.P T: +91 8941-251336, M: +91 89785 23866, F: +91 8941-251591, www.srigcsrcollege.org

Department of ELECTRONICS

# II B.Sc. IV – Semester Electronics Paper-5 Microcontrollers & Interfacing

(Study Material)

| Name of the Student | : |

|---------------------|---|

| Roll Number         |   |

| Kon Number          | • |

| Group               | : |

Year/ Semester

Prepared by: K. Venugopala Rao M.Sc.(Tech), M. Tech Lecturer in Electronics SRI GCSR COLLEGE, GMR Nagar, Rajam venugopalarao.k@sgcsrc.edu.in +91-9603803168, +91-9182061933

# **Department of ELECTRONICS**

# Dr. B. R. AMBEDKAR UNIVE RSITY-SRIKAKULAM B.Sc. ELECTRONICS SYLLABUS STRUCTURE UNDER CHOICE BASED CREDITS SYSTEM REVIEWED SYLLUBUS w.e.f. 2021-22 II B.Sc. Semester – IV Paper – V: Microcontrollers & Interfacing

# **UNIT – I: INTRODUCTION TO MICROCONTROLLERS**

Introduction, comparison of Microprocessor and microcontroller, Evolution of microcontrollers from 4-bit to 32-bit, Development tools for microcontrollers, Assembler-Compiler-Simulator/Debugger.

# <u>UNIT – II: MICROCONTROLLER ARCHITECTURE</u>

Overview and block diagram of 8051, Architecture of 8051, program counter and memory organization, Data types and directives, PSW register, Register banks and stack, pin diagram of 8051, Interrupts and timers.

# **UNIT – III: ADDRESSING MODES, INSTRUCTION SET OF 8051**

Addressing modes and accessing memory using various addressing modes, instruction set: Arithmetic, Logical, Simple bit, jump, loop and call instructions.

# **UNIT – IV: ASSEMBLE LANGUAGE PROGRAMMING**

Addition, Multiplication, Subtraction, division, arranging a given set of numbers in largest/smallest order, Timer/Counter Programming

# **UNIT – V: INTERFACING AND APPLICATION OF MICROCONTROLLER**

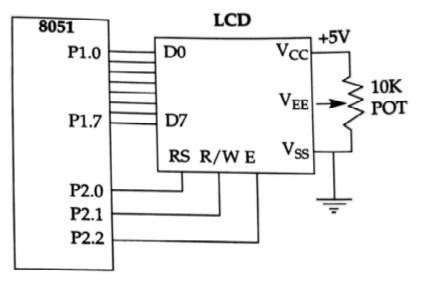

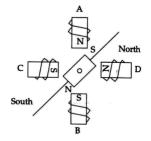

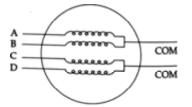

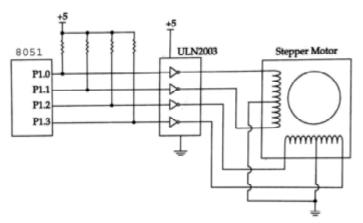

Interfacing of – PPI 8255, interfacing seven segment displays, displaying information on an LCD, control of a stepper Motor (Uni-Polar).

# MICROCONTROLLER AND INTERFACING

# UNIT I

## **Microcontroller Architecture**

#### Introduction

A microcontroller is a computer present in a single integrated circuit which is dedicated to perform one task and execute one specific application.

It contains memory, programmable input/output peripherals as well a processor. Microcontrollers are mostly designed for embedded applications and are heavily used in automatically controlled electronic devices such as cell phones, cameras, microwave ovens, washing machines, etc.

#### **Microcontrollers and Microprocessors**

A microprocessor is an integrated circuit (IC) and is a computer's central processing unit (CPU on a chip). It is a programmable multipurpose silicon chip, clock driven, register based, accepts binary data as input and provides output after processing it as per the instructions stored in the memory. It consists of Arithmetical and Logical Unit (ALU), Control Unit and Register Array.

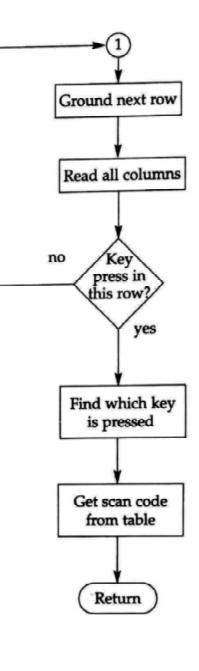

General-purpose Microprocessor System

Microcontroller

Microcontroller (MC) may be called computer on chip since it has basic features of microprocessor with internal ROM, RAM, Parallel and serial ports within single chip. Or we can say microprocessor with memory and ports is called as microcontroller. This is widely used in washing machines, vcd player, microwave oven, robotics or in industries.

The 8051 is the first microcontroller of the MCS-51 family introduced by Intel Corporation in the 1981. The 8051 family with its many enhanced members enjoys the largest market share, among the various microcontroller architectures like PIC, AVR, ARM, etc.

Microcontroller can be classified on the basis of their bits processed like 8bit MC, 16bit MC, 32bit MC. 8 bit microcontroller, means it can read, write and process 8 bit data. Ex: 8051 microcontroller. Basically 8 bit specifies the size of data bus. 8 bit microcontroller means 8 bit data can travel on the data bus or we can read, write process 8 bit data.

# **Microprocessors and Microcontrollers**

| MICROPROCESSORS                                                                                                                          | MICROCONTROLLERS                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor contains ALU, General<br>purpose registers, stack pointer, program<br>counter, clock timing circuit, interrupt<br>circuit | Microcontroller contains the circuitry<br>of microprocessor, and in addition it<br>has built in ROM, RAM, I/O Devices,<br>Timers/Counters etc. |

| It has many instructions to move data between memory and CPU                                                                             | It has few instructions to move data between memory and CPU                                                                                    |

| Few bit handling instruction                                                                                                             | It has many bit handling instructions                                                                                                          |

| Less number of pins are multifunctional                                                                                                  | More number of pins are multifunctional                                                                                                        |

| Single memory map for data and code (program)                                                                                            | Separate memory map for data and code (program)                                                                                                |

| Access time for memory and IO are more                                                                                                   | Less access time for built in memory and IO.                                                                                                   |

| Microprocessor based system requires additional hardware                                                                                 | It requires less additional hardware                                                                                                           |

| More flexible in the design point of view                                                                                                | Less flexible since the additional<br>circuits which is residing inside the<br>microcontroller is fixed for a particular<br>microcontroller    |

| Large number of instructions with flexible addressing modes                                                                              | Limited number of instructions with few addressing modes                                                                                       |

# **Evolution of Microcontroller**

The last decade has seen an exciting evolution with capabilities of microprocessors. The development of 16 and 32 bit microprocessors contributed to the growth of powerful personal computers. In the evolution of microprocessor capability, instead of focusing upon larger word widths and address spaces. The present emphasis is upon exceedingly fast real time control. The development of microcontrollers has focused upon the integration of the facilities needed to support fast control into a single chip.

Intel has introduced standard 8-bit microcontroller 8048 in 1976. In the year 1980, Intel has introduced the 8051 microcontroller, with higher performance than 8048. With the advantages of 8051, the microcontroller applications took a peak level.

Because of the advanced semiconductor technology, it has become possible to integrate more than 1,00,000 transistors onto a single silicon chip. With this Intel developed a new generation of single chip 16 bit microcontrollers called the MCS-96 (8096 family).

The Motorola Microcontroller family was first introduced to the market in 1978 and is built in the same pattern of the microprocessor 6800.

Criteria for selection of microcontroller in any embedded system is as following

- 1. Meeting the computing needs of task at hand efficiently and cost effectively

- Speed of operation

- Packing

- Power consumption

- Amount of RAM and ROM on chip

- No. of I/O pins and timers on chip

- Cost

- 2. Availability of software development tools such as compiler, assembler and debugger.

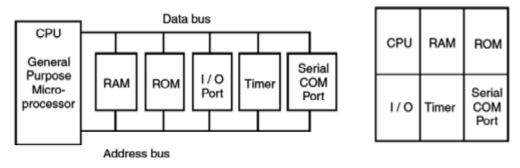

# **Types of microcontrollers**

Microcontrollers can be classified on the basis of internal bus width, architecture, memory and instruction set. The various types of microcontrollers are shown below.

# The 8, 16 and 32-bit microcontrollers

#### 8-bit microcontroller

When the ALU performs arithmetic and logical operations on a byte (8-bits), the microcontroller is an 8-bit microcontroller. The internal bus width of 8-bit microcontroller is of 8-bit. Examples of 8-bit microcontrollers are Intel 8051 family and Motorola MC68HC11 family.

#### 16-bit microcontroller

When the ALU performs arithmetic and logical operations on a word (16bits), the microcontroller is an 16-bit microcontroller. The internal bus width of 16-bit microcontroller is of 16-bit. Examples of 16-bit microcontrollers are Intel 8096 family and Motorola MC68HC12 and MC68332 families. The performance and computing capability of 16 bit microcontrollers are enhanced as compared to the 8-bit microcontrollers.

#### 32-bit microcontroller

When the ALU performs arithmetic and logical operations on a double word (32- bits), the microcontroller is an 32-bit microcontroller. The internal bus width of 32-bit microcontroller is of 32-bit. Examples of 32-bit microcontrollers are Intel 80960 family and Motorola M683xx and Intel/Atmel 251 family. The performance and computing capability of 32 bit microcontrollers are enhanced as compared to the 16-bit microcontrollers.

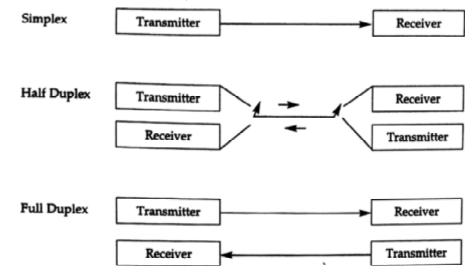

# Various features of 8051 microcontroller are given as follows.

- 8-bit CPU

- 16-bit Program Counter

- 8-bit Processor Status Word (PSW)

- 8-bit Stack Pointer

- Internal RAM of 128bytes

- Special Function Registers (SFRs) of 128 bytes

- 32 I/O pins arranged as four 8-bit ports (P0 P3)

- Two 16-bit timer/counters : T0 and T1

- Two external and three internal vectored interrupts

- One full duplex serial I/O

# Some of the microcontrollers of 8051 family are given as follows:

| DEVICE  | ON-CHIP<br>DATA<br>MEMORY<br>(RAM)<br>(bytes) | ON-CHIP<br>PROGRAM<br>MEMORY<br>(ROM)<br>(bytes) | 16-BIT<br>TIMER/COUNTER | NO. OF<br>VECTORED<br>INTERUPTS | Serial I/O |

|---------|-----------------------------------------------|--------------------------------------------------|-------------------------|---------------------------------|------------|

| 8031    | 128                                           | None                                             | 2                       | 5                               | 1          |

| 8032    | 256                                           | none                                             | 2                       | 6                               | 1          |

| 8051    | 128                                           | 4k ROM                                           | 2                       | 5                               | 1          |

| 8052    | 256                                           | 8k ROM                                           | 3                       | 6                               | 1          |

| 8751    | 128                                           | 4k EPROM                                         | 2                       | 5                               | 1          |

| 8752    | 256                                           | 8k EPROM                                         | 3                       | 6                               | 1          |

| AT89C51 | 128                                           | 4k Flash<br>Memory                               | 2                       | 5                               | 1          |

| AT89C52 | 256                                           | 8k Flash<br>memory                               | 3                       | 6                               | 1          |

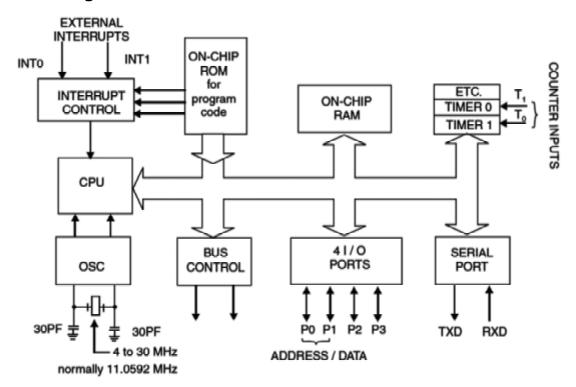

#### Block diagram of 8051

It is 8-bit microcontroller, means MC 8051 can Read, Write and Process 8 bit data. This is mostly used microcontroller in the robotics, home appliances like mp3 player, washing machines, electronic iron and industries. Mostly used blocks in the architecture of 8051 are as follows:

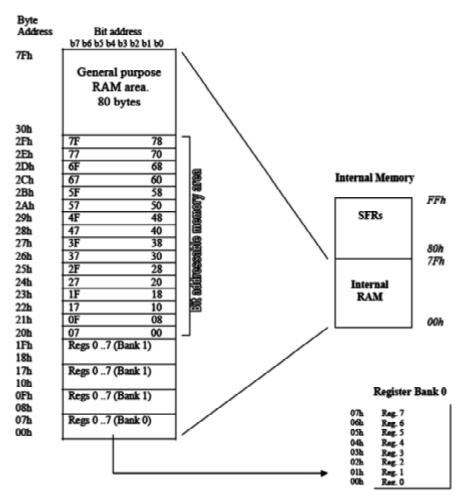

#### 128 Byte RAM for Data Storage

MC 8051 has 128 byte Random Access memory for data storage. During execution for storing the data the RAM is used. RAM consists of the register banks, stack for temporary data storage. It also consists of some special function register (SFR) which are used for some specific purpose like timer, input output ports etc. Normally microcontroller has 256 byte RAM in which 128 byte (address range 00H to 7FH) is used for user space which is normally Register banks and stack. But other 128 byte (address range 80H to FFH) RAM which consists of SFRs.

#### 4KB ROM

In 8051, 4KB read only memory (ROM) is available for program storage, addressed from 0000H to 0FFFH

#### **Timers and Counters**

Timer is which can give the delay of particular time between some events. In MC8051, two 16 bit timers are available, named as T0 (TH0, TL0) and T1 (TH1, TL1),by these timers we can give the delay of particular time. TMOD, TCON registers are used for controlling timer operation.

#### **Serial Port**

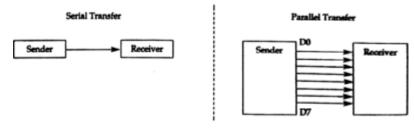

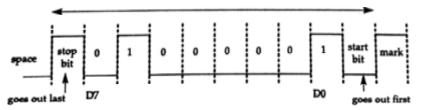

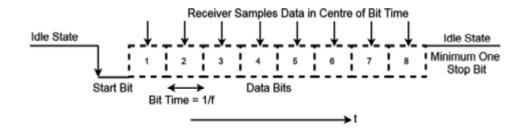

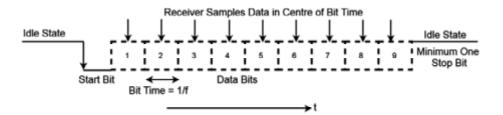

There are two pins available for serial communication TXD and RXD.

Normally TXD is used for transmitting serial data which is in SBUF register, RXD is used for receiving the serial data.

SCON register is used for controlling the operation.

#### Input Output Ports

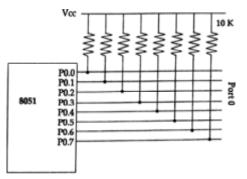

There are four input output ports available P0, P1, P2, P3. Each port is 8 bit wide.

The port 0 can perform dual works. It is also used as Lower order address bus (A0 to A7) multiplexed with 8 bit data bus P0.0 to P0.7 is AD0 to AD7 respectively the address bus and data bus is demultiplex by the ALE signal.

Port 2 can be used as I/O port as well as higher order address bus A8 to A15.

Port 3 also have dual functions it can be worked as I/O as well as each pin of P3 has specific function.

- P3.0 RXD Serial data IO

- P3.1 TXD Serial data transmit

- P3.2 INT0 External Interrupt 0

- P3.3 INT1 External Interrupt 1

- P3.4 T0 Clock input for counter 0

- P3.5 T1 Clock input for counter 1

- P3.6 WR Signal for writing to external memory

- P3.7 RD Signal for reading from external memory

When external memory is interfaced with 8051 then P0 and P2 can't be worked as I/O port they works as address bus and data bus, otherwise they can be accessed as I/O ports.

#### Oscillator

It is used for providing the clock to MC8051 which decides the speed or baud rate of MC.

We use crystal which frequency vary from 4MHz to 30 MHz, normally we use 11.0592 MHz frequency.

#### Interrupts

Interrupts are defined as requests because they can be refused (masked) if they are not used, that is when an interrupt is acknowledged. A special set of events or routines are followed to handle the interrupts. These special routines are known as or interrupt service routines (ISR).

INT0 and INT1 are the pins for external interrupts.

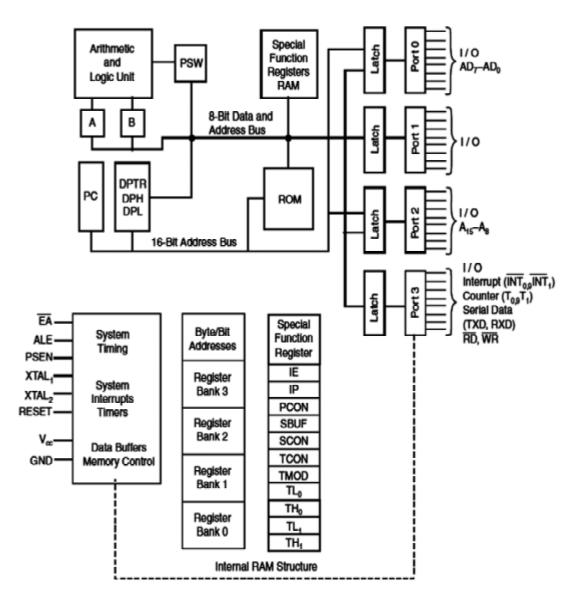

#### THE 8051 ARCHITECTURE

The 8051 MC is available in n-channel metal oxide silicon (N-MOS) and Complementary metal oxide silicon (C-MOS) construction in a variety package types. It is housed in a 40 pin DIP. It requires 5V DC for its operation.

Salient features of 8051 microcontroller are given below.

- 8 bit CPU

- 4Kbytes of internal program memory (code memory) [ROM]

- 128 bytes of internal data memory [RAM]

- 64 Kbytes of external program memory address space.

- 64 Kbytes of external data memory address space.

- 32 bi directional I/O lines (can be used as four 8 bit ports or 32 individually addressable I/O lines)

- Two 16 Bit Timer/Counter :T0, T1

- Full Duplex serial data receiver/transmitter

- Four Register banks with 8 registers in each bank.

- Sixteen bit Program counter (PC) and a data pointer (DPTR)

- 8 Bit Program Status Word (PSW)

- 8 Bit Stack Pointer

- Five vector interrupt structure (RESET not considered as an interrupt.)

- 8051 CPU consists of 8 bit ALU with associated registers like accumulator 'A', B register, PSW, SP, 16 bit program counter, stack pointer.

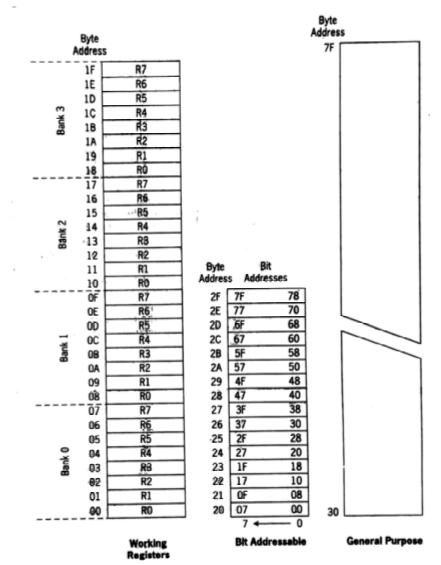

- 8051 has 128 bytes of internal RAM which is divided into

Working registers [00 - 1F]

Bit addressable memory area [20 – 2F]

General purpose memory area (Scratch pad memory) [30-7F]

8051 has 4 K Bytes of internal ROM. The address space is from 0000 to 0FFFh. If the program size is more than 4 K Bytes 8051 will fetch the code automatically from external memory.

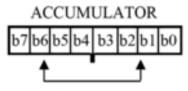

Accumulator is an 8 bit register widely used for all arithmetic and logical operations. Accumulator is also used to transfer data between external memory. B register is used along with Accumulator for multiplication and division. A and B registers together is also called MATH registers.

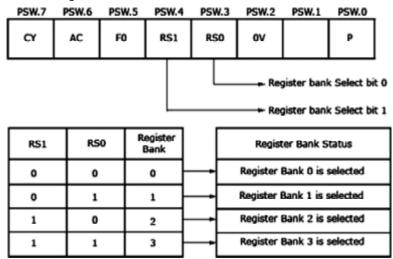

**PSW (Program Status Word) -** This is an 8 bit register which contains the arithmetic status of ALU and the bank select bits of register banks.

|   | (MSB)<br>PSW.7 | PSW.6 | PSW.5 | PSW.4 | PSW.3 | PSW.2 | PSW.1 | (LSB)<br>PSW.0 |  |

|---|----------------|-------|-------|-------|-------|-------|-------|----------------|--|

|   | CY             | AC    | FO    | RS1   | RS0   | ov    | -     | Р              |  |

| 1 | D7             | D6    | D5    | D4    | D3    | D2    | D1    | DO             |  |

- CY carry flag

- AC auxiliary carry flag

- F0 available to the user for general purpose

- RS1, RS0 register bank select bits

- OV overflow

- P parity

#### Stack Pointer (SP)

It contains the address of the data item on the top of the stack. Stack may reside anywhere on the internal RAM. On reset, SP is initialized to 07 so that the default stack will start from address 08 onwards.

#### Data Pointer (DPTR)

DPH (Data pointer higher byte), DPL (Data pointer lower byte). This is a 16 bit register which is used to furnish address information for internal and external program memory and for external data memory.

#### **Program Counter (PC)**

16 bit PC contains the address of next instruction to be executed. On reset PC will set to 0000. After fetching every instruction PC will increment by one.

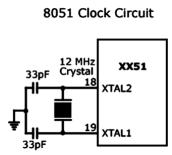

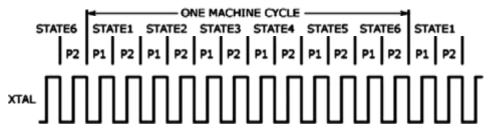

#### System Clock

The heart of 8051 is the circuitry that generates the clock pulses by which all internal operations are synchronised. Pins XTAL1 and XTAL2 are provided for connecting an oscillator. The crystal frequency is the basic internal frequency of the microcontroller. 8051 is designed to operate between 1MHz to 16MHz and generally operates with a crystal frequency 11.04962 MHz.

The time taken to complete any instruction is

called as machine cycle or instruction cycle. In 8051 one instruction cycle consists of 6 states or 12 clock cycles. Two pulses forms a state and six states forms one machine cycle.

#### System Clock

To calculate time for any instruction will be executed.

$$T_{inst} = \frac{C X 12d}{crystalfrequency}$$

Where, C is the no. of machine cycles.

Ex: for example the crystal frequency is 16 MHz, the time to execute an ADD a, R1 one cycle inst.

$$T_{inst} = \frac{1X12}{16 X10^6} = 0.75 \,\mu \,sec$$

- **Pins 1-8 : PORT 1**. Each of these pins can be configured as an input or an output.

- **Pin 9 : RESET.** A logic one on this pin disables the microcontroller and clears the contents of most registers. In other words, the positive voltage on this pin resets the microcontroller. By applying logic zero to this pin, the program starts execution from the beginning.

- **Pins10-17 : PORT 3**. Similar to port 1, each of these pins can serve as general input or output. Besides, all of them have alternative functions

- **Pin 10 : RXD.** Serial asynchronous communication input or Serial synchronous communication output.

- **Pin 11 : TXD.** Serial asynchronous communication output or Serial synchronous communication clock output.

- Pin 12 : INTO. External Interrupt 0 input

- Pin 13 : INT1. External Interrupt 1 input

- Pin 14 : T0. Counter 0 clock input

- Pin 15 : T1. Counter 1 clock input

- **Pin 16 : WR.** Write to external (additional) RAM

- Pin 17 : RD. Read from external RAM

- **Pin 18, 19 : XTAL2, XTAL1.** Internal oscillator input and output. A quartz crystal which specifies operating frequency is usually connected to these pins.

- Pin 20 : GND. Ground.

- **Pin 21-28 : Port 2.** If there is no intention to use external memory then these port pins are configured as general inputs/outputs. In case external memory is used, the higher address byte, i.e. addresses A8-A15 will appear on this port. Even though memory with capacity of 64Kb is not used, which means that not all eight port bits are used for its addressing, the rest of them are not available as inputs/outputs.

- Pin 29: PSEN. If external ROM is used for storing program then a logic zero (0) appears on it every time the microcontroller reads a byte from memory.

- **Pin 30 : ALE.** Prior to reading from external memory, the microcontroller puts the lower address byte (A0-A7) on P0 and activates the ALE output. After receiving signal from the ALE pin, the external latch latches the state of P0 and uses it as a memory chip address. Immediately after that, the ALE pin is returned its previous logic state and P0 is now used as a Data Bus.

- **Pin 31 : EA.** By applying logic zero to this pin, P2 and P3 are used for data and address transmission with no regard to whether there is internal memory or not. It means that even there is a program written to the microcontroller, it will not be executed. Instead, the program written to external ROM will be executed. By applying logic one to the EA pin, the microcontroller will use both memories, first internal then external (if exists).

- **Pin 32-39 : PORT 0.** Similar to P2, if external memory is not used, these pins can be used as general inputs/outputs. Otherwise, P0 is configured as address output (A0-A7) when the ALE pin is driven high (1) or as data output (Data Bus) when the ALE pin is driven low (0).

- **Pin 40 : VCC.** +5V power supply.

# SFR Registers

# Accumulator

This is an 8 bit register and is used to the hold result of various arithmetic and logic operations.

The accumulator, referred to as ACC or A.

MOV A, #52h - Move immediate the value 52h to the accumulator

MOV 70h, #52h - Move immediate the value 52h to Internal RAM location 70h.

# **B** Register

The B register is an SFR register at addresses F0h which is bit-addressable. The B register is used in two instructions only: i.e. MUL (multiply) and DIV (divide). The B register can also be used as a general-purpose register.

# **Program Counter**

The PC (Program Counter) is a 2 byte (16 bit) register which always contains the memory address of the next instruction to be executed. When the 8051 is reset the PC is always initialised to 0000h.

#### SFR Registers for the Internal Timer

**TCON** - The Timer Control register is an SFR at address 88h, which is bitaddressable. TCON is used to configure and monitor the 8051 timers. The TCON SFR also contains some interrupt control bits.

**TMOD** - The Timer Mode register is an SFR at address 89h and is used to define the operational modes for the timers.

**Timer 0 (T0) -** TL0 (Timer 0 Low) and TH0 (Timer 0 High) are two SFR registers addressed at 8Ah and 8Bh respectively. The two registers are associated with Timer 0.

**Timer 1 (T1) -** TL1 (Timer 1 Low) and TH1 (Timer 1 High) are two SFR registers addressed at 8Ch and 8Dh respectively. These two registers are associated with Timer 1.

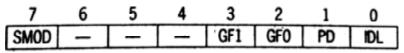

#### Power Control Register

**PCON (Power Control)** - PCON register is an SFR at address 87h. It contains various control bits including a control bit, which allows the 8051 to go to 'sleep' so as to save power when not in immediate use.

#### **Serial Port Registers**

**SCON (Serial Control)** - The SCON (Serial Control) is an SFR register located at addresses 98h, and it is bitaddressable. SCON configures the behaviour of the onchip serial port, setting up parameters such as the baud rate of the serial port, activating send and/or receive data, and setting up some specific control flags.

**SBUF (Serial Buffer)** - The SBUF (Serial Buffer) is an SFR register located at address 99h. SBUF is just a single byte deep buffer used for sending and receiving data via the on-chip serial port

#### Interrupt Registers

**IE (Interrupt Enable)** - IE (Interrupt Enable) is an SFR register at addresses A8h and is used to enable and disable specific interrupts. The MSB bit (bit 7) is used to disable all interrupts.

**IP (Interrupt Priority)** - IP (Interrupt Priority) is an SFR register at addresses B8h and it is bit addressable. The IP register specifies the relative priority (high or low priority) of each interrupt.

On the 8051, an interrupt may either be of low (0) priority or high (1) priority. .

# **Program Counter and Data Pointer**

The 8051 contains two 16-bit registers, the program counter (PC) and the data pointer (DPTR). Each is used to hold the address of a byte in memory.

#### **Program Counter**

The PC (Program Counter) is a 16 bit register which always contains the memory address of the next instruction to be executed. When the 8051 is reset the PC is always initialised to 0000h. If a instruction is executed the PC is incremented to point to the next instruction to be executed. A jump instruction (e.g. LJMP) has the effect of causing the program to branch to a newly specified location, so the jump instruction causes the PC contents to change to the new address value.

#### **Data Pointer**

The Data Pointer, DPTR, is a special 16-bit register used to address the external code or external data memory. Since the SFR registers are just 8-bits wide the DPTR is stored in two SFR registers, where DPL (82h) holds the low byte of the DPTR and DPH (83h) holds the high byte of the DPTR.

For example, for write the value 46h to external data memory location 2500h.

The following instructions are needed.

MOV A, #46h ; Move immediate 8 bit data 46h to A (accumulator)

MOV DPTR, #2500h ; Move immediate 16 bit address value 2500h to DPTR.

Now DPL holds 04h and DPH holds25h.

MOVX @DPTR, A ; Move the value in A to external RAM location 2500h.

Note: The **MOVX** (Move X) instruction is used to access external data memory.

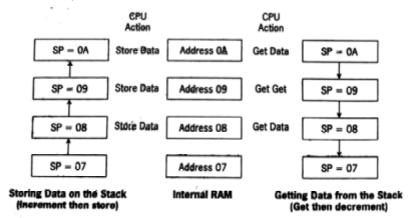

#### The Stack and the Stack Pointer

The stack refers to an area of internal RAM that is used in conjunction with certain opcode to store and retrieve data quickly. The 8-bit Stack Pointer (SP) register is used by the 8051 to hold an internal RAM address that is called the top of the stack. The address held in the SP register is the location in internal RAM where the last byte of data was stored by a stack operation.

When data is to be placed on the stack, the SP is increments before storing data on the stack so that the stack grows up as data is stored. As data is retrieved from the stack, the byte is read from the stack, and then the SP decrements to point to the next available byte of stored data.

Operation of the stack and the SP is shown in Figure. The SP is set to 07h when the 8051 is reset and can be changed to any internal RAM address by the programmer. The stack is limited in height to the size of the internal RAM. The stack has the potential to over write valuable data in the register banks, bit-addressable RAM, and scratch pad RAM areas. The programmer is responsible for making sure the stack does not grow beyond predefined bounds!

# Flags and the Program Status Word (PSW)

The 8051 has four math flags that respond automatically to the outcomes of math operations and three general-purpose user flags that can be set to 1 or cleared to 0 by the programmer as desired. The math flags include Carry (C), Auxiliary Carry (AC), Overflow (OV), and Parity (P). User flags are named FO, GFO, and GF1, they are general-purpose flags that may be used by the programmer to record some event in the program. Note that all of the flags can be set and cleared by the programmer.

The program status word is shown in Figure. The PSW contains the math flags, user program flag FO, and the register select bits that identify which of the four general-purpose register banks is currently in use by the program. The remaining two user flags, GF0 and GF1, are stored in PCON.

#### CY, the carry flag

- This flag is set whenever there is a carry out from the D7 bit.

- This flag bit is affected after an 8-bit addition or subtraction.

- It can also be set to 1 or 0 directly by an instruction such as "SETB C" and "CLR.

#### AC, the auxiliary carry flag

- If there is a carry from **D3 to D4 during an ADD or SUB** operation, this bit is set; otherwise, it is cleared.

- This flag is used by instructions that perform BCD (binary coded decimal) arithmetic.

#### P, the parity flag

- The parity flag reflects the number of 1 s in the A (accumulator) register only.

- If the A register contains an odd number of Is, then P = 1. Therefore, P = 0 if A has an even number of 1s.

#### OV, the overflow flag

- This flag is set whenever the result of a signed number operation is too large, causing the high-order bit to overflow into the sign bit.

- In general, the carry flag is used to detect errors in unsigned arithmetic operations.

- The overflow flag is only used to detect errors in signed arithmetic operations

#### Internal RAM

The 128-byte internal RAM, which is shown detail in Figure and is organized into three distinct areas.

32 bytes from address 00h to 1Fh that make up 32 working registers organized as four banks of 8 registers each. The four register banks are numbered 0 to 3 and are made up of eight registers named R0 to R7. Each register can be addressed by name (when its bank is selected) or by its RAM address. Thus R0 of bank 3 is R0 (if bank 3 is currently selected) or address 18h. Bits RS0 and RS1 in the PSW determine which bank of registers is currently in use. Register banks not selected can be used as general-purpose RAM. Bank 0 is selected on reset.

A bit-addressable area of 16 bytes occupies RAM byte addresses 20h to 2Fh, forming a total of 128 addressable bits. An addressable bit may be specified by its bit address of 00h to 7Fh. for example, bit address 4Fh is a bit 7 of byte address 29h.

A general-purpose RAM area above the bit area, from 30h to 7Fh, addressable as bytes.

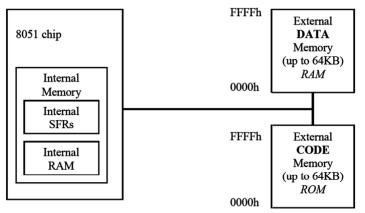

# **Memory and Register Organisation**

The 8051 has a separate memory space for code (programs) and data. The on-chip memory and external memory is as shown in figure.

8051 Memory representation

#### **External Code Memory**

The executable program code is stored in this code memory. The code memory size is limited to 64KBytes (in a standard 8051). The code memory is read-only in normal operation and is programmed under special conditions e.g. it is a PROM or a Flash RAM type of memory.

#### **External RAM Data Memory**

This is read-write memory and is available for storage of data. Up to 64KBytes of external RAM data memory is supported (in a standard 8051).

#### **Internal Memory**

The 8051's on-chip memory consists of 256 memory bytes organised as follows:

| 00h to 1Fh Register Banks             |

|---------------------------------------|

| 20h to 2Fh Bit Addressable RAM        |

| 30 to 7Fh General Purpose RAM         |

| 80h to FFh Special Function Registers |

|                                       |

#### **SFR Registers**

The SFR registers are located within the Internal Memory in the address range 80h to FFh. Not all locations within this range are defined. Each SFR has a very specific function. Each SFR has an address (within the range 80h to FFh). Some of the SFR registers are bit addressable. SFRs are accessed just like normal Internal RAM locations.

# **Internal memory**

The first 128 bytes of internal memory is organised as shown in figure, and is referred to as Internal RAM.

Organisation of Internal RAM (IRAM) memory

#### **Register banks RAM:**

32 bytes from address 00h to 1Fh that make up 32 working registers organized as four banks of 8 registers each. The four register banks are numbered 0 to 3 and are made up of eight registers named R0 to R7.

The 8051 uses 8 general-purpose registers R0 through R7 (R0, R1, R2, R3, R4, R5, R6, and R7). These registers are used in instructions such as:

ADD A, R2 ; adds the value contained in R2 to the accumulator. i.e., it adds content of 01h location to accumulator.

The following instruction has the same effect as the above instruction.

ADD A, 02h

The selection of register bank depends upon RS1 and RS0 which are in PSW.

Bit Addressable RAM: 20h to 2Fh

The 8051 supports a special feature which allows access to bit variables. That means the individual memory bits in Internal RAM can be set or cleared. The Bit Addressable area of the RAM is just 16 bytes of Internal RAM located between 20h and 2Fh. In all there are

128 bits numbered 00h to 7Fh. A bit variable can be set with a command such as SETB and cleared with a command such as CLR.

SETB 25h ; sets the bit 25h (becomes 1)

CLR 25h; clears bit 25h (becomes 0)

Note, bit 25h is actually bit b5 of Internal RAM location 24h.

#### General Purpose RAM: 30h to 7Fh

These 80 bytes of Internal RAM memory are available for general-purpose data storage.

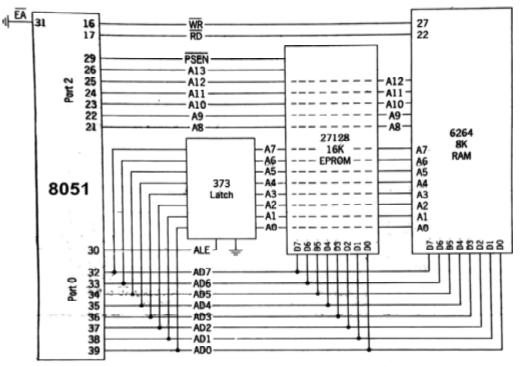

# **External Memory interfacing**

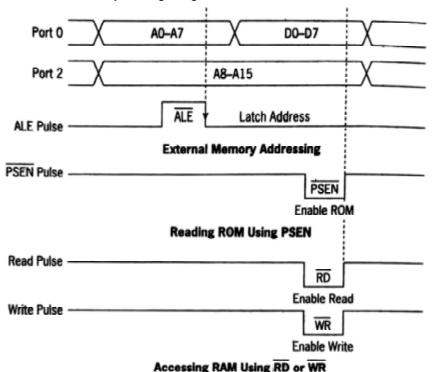

Figure 3.8 shows the connections between an 8051 and an external memory configuration consisting of 16K of EPROM and 8K of RAM. The 8051 accesses external RAM whenever certain program instructions are executed. External ROM

is accessed whenever the  $\overline{\mathsf{EA}}$  (external access) pin is connected to ground or when the PC contains an address higher than the last address in the internal 4K ROM (0FFFh). 8051 designs can thus use internal and external ROM automatically.

The lower address byte from port 0 must be latched into an external register to save the byte with help of ALE clock pulse, that provides the correct timing for the 373 data latch.

If the PSEN (program store enable) pin is low, the code byte in the ROM is placed on the data bus. If the access is for a RAM byte, the WR (write)or RD (read) pins will go low, enabling data to flow between the RAM and the data bus.

The ROM may be expanded to 64K by connecting the remaining port 2 upper address lines A14-A15 to the chip.

Fig shows external memory timing diagram.

# 8051 data type and directives

#### Data types

The 8051 microcontroller has only one data type. It is 8 bits, and the size of each register is also 8 bits. It is the job of the programmer to break down data larger than 8 bits (00 to FFH) to be processed by the CPU.

**DB** - Define a Byte - puts a byte (8-bit number) number constant at this memory location

DB 24 - It stores 18h in the memory location.

DB 24h - It stores 24h in the memory location.

DB 101101b - It stores 45 in the memory location.

**DW** - Define a Word - puts a word (16-bit number) number constant at this memory location

**DBIT** - Define a Bit, defines a bit constant, which is stored in the bit

#### Assembler directives

The following are some more widely used directives of the 8051.

# ORG (origin)

It defines the starting address for the program in program (code) memory

# EQU (equate)

This is used to define a constant without occupying a memory location. This equates a numerical value to symbol.

#### PR EQU 25h

#### **END directive**

The END directive is indicates to the assembler the end of the source (asm) file. The END directive is the last line of an 8051 program, meaning that in the source code anything after the END directive is ignored by the assembler. Some assemblers use ". END" instead of "END".

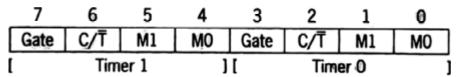

# **Counters / Timers**

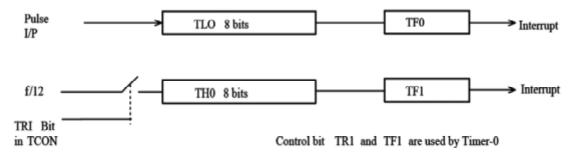

Many microcontroller applications require the counting of external events or internal time delays between actions. There are two I6-bit up counters, named T0 and TI, are provided for the general use of the programmer. Each counter may be programmed to count internal clock pulses, acting as a timer, or programmed to count external pulses as a counter.

The counters are divided into two 8-bit registers called the timer low (TLO, TL1) and high (THO, TH1) bytes. All counter action is controlled by bit states in the timer mode control register (TMOD), the timer/counter control register (TCON), and certain program instructions.

TMOD is dedicated solely to the two timers and considered as a two 4-bit registers for 2 timers. TCON has control bits and flags for the timers in the upper nibble, and control bits and flags for the external interrupts in the lower nibble.

# Timer control (TCON) special function register

This is an 8bit SFR register shown in figure, upper 4 bits for timer 0 and 1 and lower 4bits are used to control interrupts. It is a bit addressable SFR as TCON.0 to TCON.7

| TF1  | TR1  | TF0  | TR0  | IE1  | IT1  | IE0  | IT0  |

|------|------|------|------|------|------|------|------|

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

#### Timer control bits

#### TF1 - Timer 1 Overflow flag

Set when timer rolls from all 1s to 0s, Cleared when processor vectors to execute interrupt service routine located at program address 001Bh.

#### TR1- Timer 1 run control bit

Set to 1 by program to enable timer 1 to count, cleared to O by program to halt timer. Does not reset timer.

#### TF0 - Timer 0 Overflow flag

Set when timer rolls from all 1s to 0s, Cleared when processor vectors to execute interrupt service routine located at program address 000Bh.

#### TR0 - Timer 0 run control bit

Set to 1 by program to enable timer 0 to count; cleared to 0 by program to halt timer. Does not reset timer.

#### Interrupt control bits

## IE1- External interrupt 1 Edge flag

Set to 1 when a high-to low edge signal is received on port 3 pin 3.3 (INT1), Cleared to 0 when processor vectors to interrupt service routine located at program address 0013h.

#### IT1 - External interrupt 1 signal type control bit

Set to 1 by program to enable external interrupt 1 to be triggered by a falling edge signal. Set to 0 by program to enable a low-level signal on external interrupt 1 to generate an interrupt.

#### IE0 - External interrupt 0 Edge flag

Set to 1 when a high to low edge signal is received on port 3 pin 3.2 (INTO), Cleared when processor vectors to interrupt service routine located at program address 0003h.

#### IT0 - External interrupt 0 signal type control bit

Set to 1 by program to enable external interrupt 0 to be triggered by a falling edge signal. Set to 0 by program to enable a low-level signal on external interrupt O to generate an interrupt.

#### Timer mode control (TMOD) special function register

TMOD is not bit addressable

# Gate (Gating control)

Set to 1 by program to enable timer to run if bit TR in TCON is set and signal on external interrupt INT pin is high. Cleared to 0 by program to enable timer to run if bit TR in TCON is set.

# $C/\overline{T}$ (counter/ timer)

Set to 1 by program to make timer act as a counter by counting pulses from external input pin, Cleared to O by program to make timer act as a timer by counting internal frequency.

# M1 M0 (Mode selection bits)

These bits are used to select the timer mode as shown in table.

| M1 | M0         | mode   |  |

|----|------------|--------|--|

| 0  | 0          | Mode 0 |  |

| 0  | 0 1 Mode 1 |        |  |

| 1  | 0          | Mode 2 |  |

| 1  | 1          | Mode 3 |  |

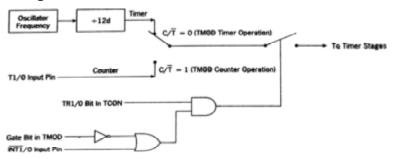

#### **Timer/counter logic**

The resultant timer clock is gated to the timer by means of the circuit shown

in Figure. The C/ $\overline{T}$  bit in the TMOD register must be set to 0. Bit TRX in the TCON register must be set to 1 (timer run), and the gate bit in the TMOD register must be 0, or external pin INTX must be a 1.

#### **Timer Modes of operation**

The timers may operate in any one of four modes that are determined by the mode bits, M1 and MO, in the TMOD register.

#### TIMER MODE 0 – 13 bit Timer/Counter

In the mode 0, the timer register is configured as a 13 bit register. The 13 bit register consists of all 8 bits of THX and the lower 5 bits of TLX. It holds value between 0000h to 1FFFh. The upper 3 bits of TLX are indetermined and should be ignored. When timer reaches its maximum value 1FFFh, it comes to initial value 0000h.

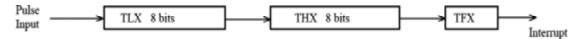

#### TIMER MODE 1 – 16 bit Timer/Counter

Mode 1 is similar to mode 0 except TLX is configured as a full 8-bit counter. Therefore it holds the value between 0000h to FFFFh. Once it is loaded, the timer must be started. When it moves from FFFFh to 0000h, it sets the timer flag (TF = 1)

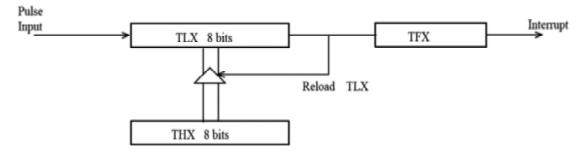

#### TIMER MODE 2 – auto reload of TL from TH

It is an 8 bit timer, therefore it allows only values between 00h to FFh. After TH is loaded with 8bit value, the timer must be started. It counts up by incrementing the TL register. When it moves from FFh to 00h, it sets the timer flag. TL is reloaded automatically with the original value, which is in the TH register.

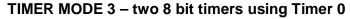

Timer 0 and 1 may be programmed to be in mode 0, 1 or 2 independently. This does not hold good for mode 3. Placing timer 1 in mode 3 causes it to stop counting. The control bit TR! And timer 1 flag bit TF1 are then used by timer 0. Timer0 in mode 3 becomes 2 completely separate 8bit counters, TL0 is controlled by gate arrangement and sets timer flag TF0 whenever it overflows. Tho receives timer clk1 under the control of TR1 and set the TF! When it over flows.

# **8051 INTERRUPTS**

#### Interrupts and polling

A single microcontroller can serve several devices. There are two ways to do that: interrupts or polling. In the interrupt method, whenever any device needs its service, the device notifies the microcontroller by sending it an interrupt signal. Upon receiving an interrupt signal, the microcontroller interrupts whatever it is doing and serves the device.

In polling, the microcontroller continuously monitors the status of a given device; when the status condition is met, it performs the service. After that, it moves on to monitor the next device until each one is serviced. it is not an efficient use of the microcontroller. The advantage of interrupts is that the microcontroller can serve many devices (not all at the same time, of course)

#### Interrupts in the 8051

The 8051 has 5 interrupts which are available to user, but including RESET, they are 6.

- Reset. When the reset pin is high, the 8051 jumps to address location 0000.

- Two interrupts from timers, one for Timer 0 and one for Timer 1.

- Two interrupts from external i/ps (INT0 &INT1), Pin numbers 12 (P3.2) and 13 (P3.3) in port 3 are for the external hardware interrupts INTO and INT1, respectively. These external interrupts are also referred to as EX1 and EX2.

- One from Serial communication port.

For every interrupt, there must be an interrupt service routine (ISR). When an interrupt is invoked, the microcontroller runs the interrupt service routine. For every interrupt, there is a fixed location in memory that holds the address of its ISR, is called the interrupt vector table, shown below.

#### Interrupt Vector Table for the 8051

| Interrupt                    | ROM  | Location (Hex) | Pin  |           |

|------------------------------|------|----------------|------|-----------|

| Reset                        |      | 0000           |      | 9         |

| External interrupt 0 (INT 0) |      | 0003           |      | P3.2 (12) |

| Timer 0 interrupt (TF0)      | 000B |                |      |           |

| External interrupt 1 (INT 1) | 0013 |                | P3.3 | (13)      |

| Timer 1 interrupt (TF1)      | 0013 |                |      |           |

| Serial COM interrupt (RI and | 0023 |                |      |           |

#### Enabling and disabling an Interrupt

Upon reset, all interrupts disabled. that is none will be responded to by the microcontroller even if they are in active. The interrupt must beenabled by the software, a SFR called IE (Interrupt Enable) is responsible for enabling (unmasking) and disabling (masking) the interrupts.

# The Interrupt Enable (IE) Special Function Register

It is Bit addressable as IE.0 to IE.7

Set to 1 by program to enable interrupt; cleared to 0 to disable interrupt.

| EA   |      | ET2  | ES   | ET1  | EX1  | ET0  | EX0  |

|------|------|------|------|------|------|------|------|

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

- IE.7 EA Disables all interrupts. If EA = 0, no interrupt is acknowledged. If EA = I, each interrupt source is individually enabled or disabled by setting or clearing its enable bit.

- IE.6 Not implemented, reserved for future use.

- IE.5 ET2 reserved for future use.

- IE.4 ES Enables or disables the serial port interrupt.

- IE.3 ET1 Enables or disables Timer I overflow interrupt.

- IE.2 EX1 Enables or disables external interrupt 1.

- IE.1 ET0 Enables or disables Timer 0 overflow interrupt.

- IE.0 EX0 Enables or disables external interrupt 0.

# The Interrupt Priority (IP) Special Function Register

It is a Bit addressable as IP0 to IP7

Interrupt register IP determines, whether an interrupt has highest priority or lowest priority. Bit set to 1, indicates higher priority and bit cleared to 0, and indicates lower priority. Lower priority interrupt continues after the higher is finished. If two interrupts with same priority occur at same time, then the following level can be used.

| Interrupt       |         |         |      |      | <u>Prio</u> | <u>ity</u> |      |

|-----------------|---------|---------|------|------|-------------|------------|------|

| External inter  |         | Highest |      |      |             |            |      |

| Timer/counte    | TF0)    | -       |      |      |             |            |      |

| External inter  | rrupt 1 |         | -    |      |             |            |      |

| Timer/counte    | TF1)    | -       |      |      |             |            |      |

| Serial port inf |         | Low     | est  |      |             |            |      |

| —               |         |         |      |      | PX1         | PT0        | PX0  |

| bit7 b          | oit6    | bit5    | bit4 | bit3 | bit2        | bit1       | bit0 |

- Bit 7 Not implemented.

- Bit 6 Not implemented.

- Bit 5 PT2 Reserved for future use.

- Bit 4 PS Priority of serial port interrupt. 1= high, 0=low

- Bit 3 PT1 Priority of timer 1 overflow interrupt. 1= high, 0=low

- Bit 2 PXI Priority of external interrupt 1. 1= high, 0=low

- Bit 1 PT0 Priority of timer 0 overflow interrupt. 1= high, 0=low

- Bit 0 PXO Priority of external interrupt 0. 1= high, 0=low

#### Steps in executing an interrupt

Upon activation of an interrupt, the microcontroller goes through the following steps.

- 1. It finishes the present executing instruction and saves the address of the next instruction (PC) on the stack.

- 2. It jumps to a fixed location in memory address of the interrupt service routine.

- 3. The microcontroller gets the address of the ISR from the interrupt vector table and jumps to it, It starts to execute the interrupt service subroutine until it reaches the last instruction of the subroutine, which is RETI (return from interrupt).

- 4. Upon executing the RETI instruction, the microcontroller returns to the place where it was interrupted. First it gets the program counter (PC) address from the stack, then it starts to execute from that address.

# UNIT II

# ADDRESSING MODES – INSTRUCTION SET

#### **Addressing Modes**

The way of data source or destination addresses (operands) are specified in the mnemonic, that means the way of data determines within the instruction is called addressing mode. There are a number of addressing modes available to the 8051 instruction set, as follows:

Immediate Addressing

**Register Addressing**

**Direct Addressing**

Indirect Addressing

**Relative Addressing**

Long Addressing

Indexed Addressing

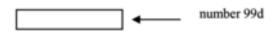

#### Immediate Addressing

Immediate addressing means that the operand is the data value to be used.

Ex: MOV A, #99d - Moves the value 99 into the accumulator.

Accumulator

The # symbol tells the assembler that the immediate addressing mode is to be used.

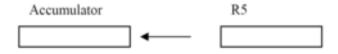

#### **Register Addressing**

One of the eight general-registers, R0 to R7, can be specified as the instruction operand.

Ex: ADD A, R5 - the contents of R5 is added to the accumulator.

#### **Direct Addressing**

Direct addressing means that the operand specifies with RAM address

Ex: MOV A, 47h

The content of RAM address 47h is store in the accumulator.

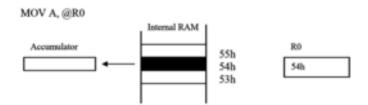

## **Indirect Addressing**

Indirect addressing provides a powerful addressing capability, An example instruction, which uses indirect addressing, is as follows:

MOV A, @R0

Note the @ symbol indicated that the indirect addressing mode is used.

The content of address location which is stored in R0 is moved to the accumulator.

#### **Relative Addressing**

This is a special addressing mode used with certain jump instructions. The relative

address, is an 8-bit signed number, which is automatically added to the PC to make the address of the next instruction. The 8-bit signed offset value gives an address range of + 127 to -128 locations.

Ex: SJMP LABEL\_X

# Long Addressing

The long addressing mode within the 8051 is used with the instructions LJMP and

LCALL. The address specifies a full 16 bit destination address so that a jump or a call

can be made to a location within a 64KByte code memory space.

Ex: LJMP 5000h ; full 16 bit address is specified in operand

# **Indexed Addressing**

With indexed addressing a separate register, either the program counter, PC, or the

data pointer DTPR, is used as a base address and the accumulator is used as an offset

address. The effective address is formed by adding the value from the base address to

the value from the offset address.

# Ex: MOVC A, @A+DPTR

MOVC is a move instruction, which moves data from the external code memory space. The address operand in this example is formed by adding the content of the DPTR register to the accumulator value.

# **Number Representation for Different Bases**

The following is an example showing the decimal number 46 represented in different number bases:

46d - 46 decimal

2Eh - 2Eh is 46 decimal represented as a hex number

560 - 56o is 46 decimal represented as an octal number

101110b - 101110b is 46 decimal represented as a binary number.

**Note:** A number must be started with digit of a hexadecimal number. For example the hexadecimal number A5h is illegally represented and should be represented as 0A5h.

The Arithmetic Operators : The arithmetic operators are:

+ add

\*

- subtract

- multiply

- / divide

- MOD modulo (result is the remainder following division)

The Logical Operators: The logical operators are:

- AND Logical AND

- OR Logical OR

- XOR Logical XOR (exclusive OR)

- NOT Logical NOT

# **Types of Instructions**

The instructions of 8051 can be broadly classified under the following headings.

- Data transfer instructions

- Arithmetic instructions

- Logical instructions

- Branch instructions

- Subroutine instructions

#### Data Transfer instructions

Many computer operations are concerned with moving data from one location to another. The 8051 uses five different types of instruction to move data.

- MOV

- MOVX

- MOVC

- PUSH and POP

- XCH

#### MOV

The MOV instruction is concerned with moving data internally, i.e. between Internal RAM, SFR registers, general registers etc. MOVX and MOVC are used in accessing external memory data.

Syntax - MOV destination source

The instruction copies data from a defined source location to a destination location.

MOV R2, #80h - Move immediate data value 80h to register R2

MOV R4, A - Copy data from accumulator to register R4

MOV DPTR, #0F22Ch - Move immediate value F22Ch to the DPTR register

MOV R2, 80h - Copy data from 80h (Port 0 SFR) to R2

MOV 52h, #52h - Copy immediate data value 52h to RAM location 52h

MOV 52h, 53h - Copy data from RAM location 53h to RAM 52h

MOV A, @R0 - Copy contents of location addressed in R0 to A (indirect addressing)

#### MOVX

The MOVX instruction is used to access the external data memory (X indicates eXternal memory access). All external moves must work through the A register (accumulator).

MOVX @DPTR, A - Copy data from A to the address specified in DPTR MOVX A, @DPTR - Copy data from address specified in DPTR to A

# MOVC

The MOVC instruction is used to read data from the external code memory (ROM). Like the MOVX instruction the DPTR register is used as the indirect address register.

MOV DPTR, # 2000h - Copy the data value 2000h to the DPTR register

MOV A, #80h - Copy the data value 80h to register A

MOVC A, @A+DPTR - Copy the contents of the address 2080h (2000h + 80h) to register A

**Note**: For the MOVC the program counter, PC, can also be used to form the address.

# **PUSH and POP**

PUSH and POP instructions are used with the stack only. The SFR register SP contains the current stack address.

PUSH 4Ch - SP is incremented. Contents of RAM location 4Ch is saved to the stack.

PUSH 00h - The content of R0 (which is at 00h in RAM) is saved to the stack.

POP 80h - The data from current SP address is copied to 80h and SP is decremented.

# ХСН

A special XCH (eXCHange) instruction will swap the data between source and destination. XCH instructions must use register A. XCHD is a special case of the exchange instruction where just the lower nibbles are exchanged.

XCH A, R3 - Exchange bytes between A and R3

XCH A,  $@\,\text{R0}$  - Exchange bytes between A and RAM location whose address is in R0

XCH A, A0h - Exchange bytes between A and RAM location A0h (SFR port 2)

#### Arithmetic instructions

Some flags within the PSW, i.e. C, AC, OV, P, are utilised in many of the arithmetic instructions.

The arithmetic instructions are

- Addition

- Subtraction

- Increment/decrement

- Multiply/divide

- Decimal adjust

#### Addition

Register A (the accumulator) is used to hold the result of any addition operation.

The ADDC instruction is used to include the carry bit in the addition process.

ADD A, #25h - Adds the number 25h to A, putting sum in A

ADD A, R3 - Adds the register R3 value to A, putting sum in A

ADDC A, #55h - Add contents of A, the number 55h, the carry bit; and put the sum in A

ADDC A, R4 - Add the contents of A, the register R4, the carry bit; and put the sum in A.

#### Subtraction

Computer subtraction can be achieved using 2's complement arithmetic. Most computers also provide instructions to directly subtract signed or unsigned numbers. The accumulator A will contain the result (difference) of the subtraction operation. The C (carry) flag is treated as a borrow flag, which is always subtracted from the minuend during a subtraction operation.

SUBB A, #55d - Subtract the number 55 (decimal) and the C flag from A; and put the result in A.

SUBB A, R6 - Subtract R6 the C flag from A; and put the result in A.

SUBB A, 58h - Subtract the number in RAM location 58h and the C flag From A; and put the result in A.

#### Increment/Decrement

The increment (INC), simply adds a binary 1 to a number while a decrement (DEC) instruction subtracts a binary 1 from a number.

INC R7 - Increment register R7

INC A - Increment A

INC @R1 - Increment the number which is the content of the address in R1

DEC A - Decrement register A

DEC 43h - Decrement the number in RAM address 43h

INC DPTR - Increment the DPTR register

#### **Multiply / Divide**

The 8051 supports 8-bit multiplication and division. The arithmetic is relatively fast since multiplication and division are implemented as single instructions. For the MUL or DIV instructions the A and B registers must be used and only unsigned numbers are supported.

#### **Multiplication**

The MUL instruction is used as follows,

MUL AB - Multiply A by B.

The resulting product resides in registers A and B, the low-order byte is in A and the high order byte is in B.

#### Division

The DIV instruction is used as follows,

DIV AB - A is divided by B.

The remainder is put in register B and the integer part of the quotient is put in register A.

## **Decimal Adjust**

The 8051 performs all arithmetic in binary numbers (i.e. it does not support BCD arithmetic). If two BCD numbers are added then the result can be adjusted by using the DA, decimal adjust, instruction.

DA A - Decimal adjust A following the addition of two BCD numbers.

#### Logical instructions

#### **Boolean Operations**

Most control applications implement control logic using Boolean operators to act on the data. Most microcomputers provide a set of Boolean instructions that act on byte level data. However, the 8051 additionally provides Boolean instruction which can operate on bit level data.

The following Boolean operations can operate on byte level or bit level data:

- ANL Logical AND

- ORL Logical OR

- CPL Complement (logical NOT)

- XRL Logical XOR (exclusive OR)

#### Logical operations at the BYTE level

ANL A, #55h - AND each bit in A with corresponding bit in number 55h, leaving the result in A.

ANL 42h, R4 - AND each bit in RAM location 42h with corresponding bit in R4, leaving the result in RAM location 42h.

ORL A, @R1 - OR each bit in A with corresponding bit in the number whose address is contained in R1 leaving the result in A.

XRL R4, 80h - XOR each bit in R4 with corresponding bit in RAM location 80h (port 0), leaving result in A.

CPL R0 - Complement each bit in R0

#### Logical operations at the BIT level

SETB 2Fh - Bit 7 of Internal RAM location 25h is set

CLR C - Clear the carry flag (flag =0)

CPL 20h - Complement bit 0 of Internal RAM location 24h

MOV C, 87h - Move to carry flag the bit 7of Port 0 (SFR at 80h)

ANL C,90h - AND C with the bit 0 of Port 1 (SFR at 90)

ORL C, 91h - OR C with the bit 1 of Port 1 (SFR at 90)

#### **Rotate Instructions**

The ability to rotate the A register (accumulator) data is useful to allow examination of individual bits. The options for such rotation are as follows:

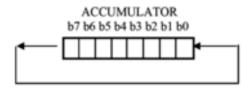

#### RL A ; Rotate A one bit to the left. Bit 7 rotates to the bit 0 position

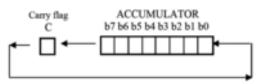

RLC A ; The Carry flag is used as a ninth bit in the rotation loop

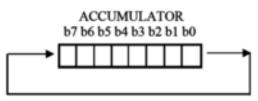

RR A; Rotates A to the right (clockwise)

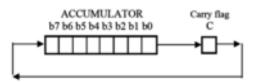

RRC A; Rotates to the right and includes the carry bit as the 9th bit.

#### Swap

The Swap instruction swaps the accumulator's high order nibble with the low-order nibble using the instruction SWAP A

high nibble low nibble

#### **Program Control Instructions (Branch control instructions)**

Branch control instructions alters the execution sequency.

The 8051 supports three kinds of jump instructions.

- LJMP

- SJMP

- AJMP

#### LJMP

LJMP (long jump) causes the program to jump to any location within the 64KByte program space.

LJMP 0F200h - Jump to address 0F200h

LJMP @A+DPTR - Jump to address which is the sum of DPTR and Reg. A

#### SJMP

SJMP (short jump) uses a singe byte address. This address is a signed 8-bit number and allows the program to branch to a distance -128 bytes back from the current PC address or +127 bytes forward from the current PC address.

#### AJMP

This is a special 8051 jump instruction, which allows a jump with a 2KByte address boundary.

#### Subroutines and program flow control

A subroutine is called using the LCALL or the ACALL instruction.

#### LCALL

This instruction is used to call a subroutine at a specified address. The address is 16 bits long so the call can be made to any location within the 64KByte memory space. When a LCALL instruction is executed the current PC content is automatically pushed onto the stack of the PC. When the program returns from the subroutine the PC contents is returned from the stack so that the program can resume operation from the point where the LCALL was made

The return from subroutine is achieved using the RET instruction.

#### ACALL

The ACALL instruction is logically similar to the LCALL but has a limited address range similar to the AJMP instruction.

#### Program control using conditional jumps

Most 8051 jump instructions use an 8-bit destination address, based on relative addressing, i.e. addressing within the range -128 to +127 bytes. When using a conditional jump instruction the programmer can simply specify a program label or a full 16-bit address for the conditional jump instruction's destination. The assembler will position the code and work out the correct 8-bit relative address for the instruction.

JZ LABEL - Jump to LABEL, if accumulator is equal to zero

JNZ LABEL - Jump to LABEL if accumulator is not equal to zero

JNC LABEL - Jump to LABEL if the carry flag is not set

DJNZ R2, LABEL - Decrement R2 and jump to LABEL if the resulting value of R2 is not zero.

CJNE R1, #55h, LABEL - Compare the magnitude of R1 and the number 55h and jump to LABEL if the magnitudes are not equal.

## **Data Transfer Instructions**

| MOV A, Rn            | : | A Rn                                                             |

|----------------------|---|------------------------------------------------------------------|

| MOV A, direct        | : | A (direct)                                                       |

| MOV A, @Ri           | : | A 🔜 @Ri                                                          |

| MOV A, #data         | : | A 🗾 data                                                         |

| MOV Rn, A            | : | Rn 🗾 A                                                           |

| MOV Rn, direct       | : | Rn 📰 (direct)                                                    |

| MOV Rn, #data        | : | Rn 💶 data                                                        |

| MOV direct, A        | : | (direct) A                                                       |

| MOV direct, Rn       | : | (direct) Rn                                                      |

| MOV direct1, direct2 | : | (direct1) (direct2)                                              |

| MOV direct, @Ri      | : | (direct) @Ri                                                     |

| MOV direct, #data    | : | (direct) #data                                                   |

| MOV @Ri, A           | : | @Ri A                                                            |

| MOV @Ri, direct      | : | @Ri (direct)                                                     |

| MOV @Ri, #data       | : | @Ri 💶 data                                                       |

| MOV DPTR, #data16    | : | DPTR 💼 data16                                                    |

| MOVC A, @A+DPTR      | : | A Code byte pointed by A + DPTR                                  |

| MOVC A, @A+PC        | : | A Code byte pointed by A + PC                                    |

| MOVC A, @Ri          | : | A Code byte pointed by Ri 8-bit address)                         |

| MOVX A, @DPTR        | : | A External data pointed by DPTR                                  |

| MOVX @Ri, A          | : | @Ri A (External data - 8bit address)                             |

| MOVX @DPTR, A        | : | @DPTR Mathematical data - 16bit address)                         |

| PUSH direct          | : | (SP) (direct)                                                    |

| POP direct           | : | (direct) (SP)                                                    |

| XCH Rn               | : | Exchange A with Rn                                               |

| XCH direct           | : | Exchange A with direct byte                                      |

| XCH @Ri              | : | Exchange A with indirect RAM                                     |

| XCHD A, @Ri          | : | Exchange least significant nibble of A with that of indirect RAM |

## **Arithmetic Instructions**

| ADD A, Rn      | : | A 🗾 A + Rn                 |

|----------------|---|----------------------------|

| ADD A, direct  | : | A A + (direct)             |

| ADD A, @Ri     | : | A 💶 A + @Ri                |

| ADD A, #data   | : | A A + data                 |

| ADDC A, Rn     | : | A A + Rn + C               |

| ADDC A, direct | : | A A + (direct) + C         |

| ADDC A, @Ri    | : | A 💶 A + @Ri + C            |

| ADDC A, #data  | : | A 🔜 A + data + C           |

| DA A           | : | Decimal adjust accumulator |

| DIV AB         | : | Divide A by B              |

|                |   | A quotient<br>B remainder  |

| DEC A          | : | A 🛛 A -1                   |

| DEC Rn         | : | Rn 🔲 Rn - 1                |

| DEC direct     | : | (direct) (direct) - 1      |

| DEC @Ri        | : | @Ri 🔜 @Ri - 1              |

| INC A          | : | A A+1                      |

| INC Rn         | : | Rn 📰 Rn + 1                |

| INC direct     | : | (direct) (direct) + 1      |

| INC @Ri        | : | @Ri 📰 @Ri +1               |

| INC DPTR       | : | DPTR DPTR +1               |

| MUL AB         | : | Multiply A by B            |

|                |   | A low byte (A*B)           |

|                |   | B high byte (A* B)         |

| SUBB A, Rn     | : | A 🔜 A - Rn - C             |

| SUBB A, direct | : | A A - (direct) - C         |

| SUBB A, @Ri    | : | A 🔜 A - @Ri - C            |

| SUBB A, #data  | : | A 🔜 A - data - C           |

# **Logical Instructions**

| ANL A, Rn                                                                            | :                                     | A 🔜 A AND Rn                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANL A, direct                                                                        | :                                     | A AND (direct)                                                                                                                                                                                                                      |

| ANL A, @Ri                                                                           | :                                     | A 🔜 A AND @Ri                                                                                                                                                                                                                       |

| ANL A, #data                                                                         | :                                     | A AND data                                                                                                                                                                                                                          |

| ANL direct, A                                                                        | :                                     | (direct) (direct) AND A                                                                                                                                                                                                             |

| ANL direct, #data                                                                    | :                                     | (direct) (direct) AND data                                                                                                                                                                                                          |

| CLR A                                                                                | :                                     | A 00H                                                                                                                                                                                                                               |

| CPL A                                                                                | :                                     | A A                                                                                                                                                                                                                                 |

| ORL A, Rn                                                                            | :                                     | A 🔜 A OR Rn                                                                                                                                                                                                                         |

| ORL A, direct                                                                        | :                                     | A A OR (direct)                                                                                                                                                                                                                     |

| ORL A, @Ri                                                                           | :                                     | A A OR @Ri                                                                                                                                                                                                                          |

| ORL A, #data                                                                         | :                                     | A A OR data                                                                                                                                                                                                                         |

| ORL direct, A                                                                        | :                                     | (direct) (direct) OR A                                                                                                                                                                                                              |

|                                                                                      |                                       |                                                                                                                                                                                                                                     |

| ORL direct, #data                                                                    | :                                     | (direct) 🔲 (direct) OR data                                                                                                                                                                                                         |

| ORL direct, #data<br>RL A                                                            | :                                     | (direct) (direct) OR data<br>Rotate accumulator left                                                                                                                                                                                |

|                                                                                      | :<br>:<br>:                           |                                                                                                                                                                                                                                     |

| RL A                                                                                 | :<br>:<br>:                           | Rotate accumulator left<br>Rotate accumulator left through                                                                                                                                                                          |

| RL A<br>RLC A                                                                        | ::                                    | Rotate accumulator left<br>Rotate accumulator left through<br>carry                                                                                                                                                                 |

| RL A<br>RLC A<br>RR A                                                                | ::                                    | Rotate accumulator left<br>Rotate accumulator left through<br>carry<br>Rotate accumulator right<br>Rotate accumulator right through                                                                                                 |

| RL A<br>RLC A<br>RR A<br>RRC A                                                       | :<br>:<br>:<br>:                      | Rotate accumulator left<br>Rotate accumulator left through<br>carry<br>Rotate accumulator right<br>Rotate accumulator right through<br>carry                                                                                        |

| RL A<br>RLC A<br>RR A<br>RRC A<br>SWAP A                                             | :<br>:<br>:<br>:<br>:                 | Rotate accumulator left<br>Rotate accumulator left through<br>carry<br>Rotate accumulator right<br>Rotate accumulator right through<br>carry<br>Swap nibbles within accumulator                                                     |

| RL A<br>RLC A<br>RR A<br>RRC A<br>SWAP A<br>XRL A, Rn                                | :<br>:<br>:<br>:<br>:                 | Rotate accumulator left<br>Rotate accumulator left through<br>carry<br>Rotate accumulator right<br>Rotate accumulator right through<br>carry<br>Swap nibbles within accumulator<br>A A EXOR Rn                                      |

| RL A<br>RLC A<br>RR A<br>RRC A<br>SWAP A<br>XRL A, Rn<br>XRL A, direct               | : : : : : : : : : : : : : : : : : : : | Rotate accumulator left<br>Rotate accumulator left through<br>carry<br>Rotate accumulator right<br>Rotate accumulator right through<br>carry<br>Swap nibbles within accumulator<br>A A EXOR Rn<br>A A EXOR (direct)                 |

| RL A<br>RLC A<br>RR A<br>RRC A<br>SWAP A<br>XRL A, Rn<br>XRL A, direct<br>XRL A, @Ri | : : : : : : : : : : : : : : : : : : : | Rotate accumulator left<br>Rotate accumulator left through<br>carry<br>Rotate accumulator right<br>Rotate accumulator right through<br>carry<br>Swap nibbles within accumulator<br>A A EXOR Rn<br>A A EXOR (direct)<br>A A EXOR @Ri |

## **Boolean Variable Instructions**

| CLR C   | : | C-bit 0 |

|---------|---|---------|

| CLR bit | : | bit 0   |

| SET C   | : | C 1     |

| SET bit     | : bit 1     |

|-------------|-------------|

| CPL C       | C C-bit     |

| CPL bit     | : bit bit   |

| ANL C, /bit | C C. bit    |

| ANL C, bit  | : C C. bit  |

| ORL C, /bit | : C C + bit |

| ORL C, bit  | : C C + bit |

| MOV C, bit  | : C bit     |

| MOV bit, C  | : bit C     |

# **Program Branching Instructions**

| ACALL addr11         | : PC + 2 (SP) ; addr 11 PC                         |

|----------------------|----------------------------------------------------|

| AJMP addr11          | : Addr11 PC                                        |

| CJNE A, direct, rel  | : Compare with A, jump (PC + rel) if not equal     |

| CJNE A, #data, rel   | : Compare with A, jump (PC + rel) if not equal     |

| CJNE Rn, #data, rel  | : Compare with Rn, jump (PC + rel) if not equal    |

| CJNE @Ri, #data, rel | : Compare with @Ri A, jump (PC + rel) if not equal |

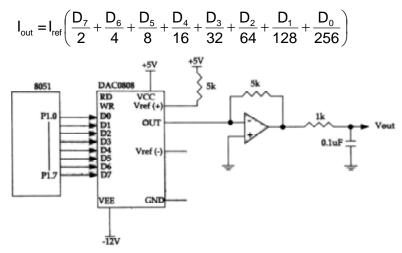

| DJNZ Rn, rel         | : Decrement Rn, jump if not zero                   |